# Effects of Post Annealing and Oxidation Processes on the Removal of Damage Generated during the Shallow Trench Etch Process

Young-Jun LEE<sup>1</sup>, Soon-Won HWANG<sup>1</sup>, Kyung-Hee OHO<sup>2</sup>, Jung-Yong LEE<sup>3</sup> and Geun-Young YEOM<sup>1</sup>

(Received July 14, 1998; accepted for publication October 19, 1998)

In this study,  $0.3-0.5~\mu m$  deep silicon trenches were etched using  $Cl_2/10\%N_2$  and  $Cl_2/50\%HBr$  inductively coupled plasmas, and the defects remaining on the etched silicon trench surfaces and the effects of various annealing and oxidation on the removal of the defects were studied. High resolution transmission electron microscopy was used to investigate the degree of remaining defects and X-ray photoelectron spectroscopy was also used to investigate surface contamination of the etched silicon wafers. Defects were found on the silicon trench surfaces etched using both  $Cl_2/10\%N_2$  and  $Cl_2/50\%HBr$ . A thermal oxidation of 200 Å at the temperature up to  $1,100^{\circ}C$  did not remove the remaining defects completely and more defects were remained on the silicon trench etched using  $Cl_2/10\%N_2$ . More defects remaining on the oxidized silicon trench for  $Cl_2/10\%N_2$  appear to be related to the formation of silicon oxynitride on the silicon trench etched in  $Cl_2/10\%N_2$ , therefore, forming less thermal oxide during the oxidation process. The annealing of the etched silicon trenches from  $900^{\circ}C$  to  $1,000^{\circ}C$  for 30 min in  $N_2$  also decreased the number of defects, however, to remove the defects formed in our experiments, the annealings at the temperature higher than  $1,000^{\circ}C$  in  $N_2$  for 30 min appears to be required. A combination process of annealing at  $1,000^{\circ}C$  and oxidation at  $900^{\circ}C$  was also effective in removing the defects completely.

KEYWORDS: STI, silicon trench etching, inductively coupled plasma, damage, oxidation, annealing

#### 1. Introduction

Shallow trench isolation (STI) is a promising key technology for the deep submicron device isolation of silicon integrated circuits which replaces the conventional local oxidation of silicon (LOCOS) type of isolation.<sup>1–5)</sup> This coupled with the additional advantages of better planarity, smaller active area encroachment, and smaller junction edge capacitance enabling the scaling of active area pitches down to  $0.5 \, \mu \mathrm{m}$  regime.

For the trench isolation, the control of the trench profile angle to refill the CVD oxide easily and the roundness of the trench bottom corners are some of important factors to obtain superior isolation characteristics of STI. Currently, chlorine and bromine-based plasmas are widely studied in the trench etch processes from the experience of the anisotropic etching of highly doped gate polysilicon. <sup>6,7)</sup> However, the most studies are concentrated on controlling the etch profile and selectivity while maintaining the etch uniformity, and the effects of these gas combinations on the remaining defects during the shallow trench etch processes are not well investigated.

The purpose of this work is to identify the possible defects on the submicron silicon trenches etched using  $\text{Cl}_2/\text{N}_2$  and  $\text{Cl}_2/\text{HBr}$  plasmas, and also to study the effects of the following oxidation or annealing processes respectively on the removal of the defects. By distinguishing the effects of gas combinations on the defects and the degree of removal of them by the following processes, the better control of the shallow trench isolation processes could be obtained.

# 2. Experimental

A home-made inductively coupled plasma(ICP) etching reactor with a 3.5 turn and 0.6 cm diameter spiral copper coil on top of a 25 cm diameter anodized Al chamber separated by a 1 cm thick quartz window was used in this experiment. The rf power of 13.56 MHz was applied to the coil to induce inductively coupled plasmas. Another 13.56 MHz rf power was applied to the 5 inch diameter and water cooled (25°C)

substrate to induce bias voltages to the wafer. The dc-self bias voltage was measured between the substrate and matching network using a high voltage probe (Tektronix P6015A). The distance between the quartz window and the substrate was kept at 7 cm.

Before etching silicon trenches, the silicon wafers were patterned with the 100 Å thermal oxide/2,000 Å silicon nitride having 0.3–0.8  $\mu$ m linewidths. 0.3–0.5  $\mu$ m deep silicon trenches were etched using various mixture of Cl<sub>2</sub>/HBr and Cl<sub>2</sub>/N<sub>2</sub> while keeping the total pressure at 10 mTorr. The gas mixtures were prepared by a gas density ratio method, that is, to prepare Cl<sub>2</sub>/50%HBr, Cl<sub>2</sub> was flowed to the chamber to make 5 mTorr and HBr was added to make total pressure 10mTorr while the conductance was kept same. Most of the studies on the damage during the etchings and the effects of the following annealing and oxidation processes were carried out using the Cl<sub>2</sub>/50%HBr and Cl<sub>2</sub>/10%N<sub>2</sub> gas chemistries. The etch conditions and etch rates for these gas chemistries are listed in Table I.

The defects formed on the etched silicon trenches were observed using high-resolution transmission electron microscopy (HRTEM; JEOL JEM 2000 EX). Various annealing and oxidation processes were conducted after the silicon trench etching to investigate the effects of post-etch annealing or oxidation on the removal of the defects formed during the silicon trench etching. Annealing processes were performed in the atmospheric pressure with N<sub>2</sub> (flow rate: 30 slm) from 900°C to 1,000°C for 30 min and oxidation processes in the atmospheric pressure with O<sub>2</sub> (flow rate: 50 slm) from 900°C to 1,100°C for the time to form 200-Å-thick SiO<sub>2</sub> on the blank silicon wafers. Prior to the annealing processes, all the samples were treated in a 10:1 diluted HF solution for 30s to remove residues possibly formed during the etching. Remaining physical defects on the sidewalls, bottoms, and corners of the annealed/oxidized silicon trenches were observed using the HRTEM. The chemical composition and binding states of the remaining residue on the blank etched silicon surfaces were investigated as a function of gas combinations using

<sup>&</sup>lt;sup>1</sup>Department of Materials Engineering, Sungkyunkwan University, Suwon, Kyunggi-do, 440-746, Korea

<sup>&</sup>lt;sup>2</sup>National Institute of Technology and Quality, Kwacheon, Kyunggi-do, 427-010, Korea

<sup>&</sup>lt;sup>3</sup>Department of Materials Engineering, Korea Advanced Institute of Science and Technology, Taejon, 305-701, Korea

Table I. The etch conditions and etch rates for gas chemistries of  $\text{Cl}_2/\text{50\%HBr}$  and  $\text{Cl}_2/\text{10\%N}_2$  used in the experiment.

| Chemistry         | Cl <sub>2</sub> /50%HBr | Cl <sub>2</sub> /10%N <sub>2</sub> |

|-------------------|-------------------------|------------------------------------|

| Inductive power   | 400 W                   | 400 W                              |

| Dc-bias voltage   | -100 V                  | -100  V                            |

| Pressure          | 10 mTorr                | 10 mTorr                           |

| Wafer temperature | 25°C                    | 25°C                               |

| Etch rate         | 3,000 Å/min             | 2,800 Å/min                        |

X-ray photoelectron spectroscopy (XPS; Fisons system; ES-CALAB 220i). The analysis utilized a aluminum source and 90° electron take-off angle.

#### 3. Results and Discussion

Silicon shallow trench etching using inductively coupled  $\text{Cl}_2/\text{HBr}$  and  $\text{Cl}_2/\text{N}_2$  plasmas has been investigated as a function of gas combination, inductive power, and bias voltage and is described in details elsewhere.<sup>8)</sup> In case of the trench etch profiles, the addition of HBr (50%) and N<sub>2</sub> (10%) to chlorine has improved the etch profile and the etch profiles of the silicon etched in  $\text{Cl}_2/10\%\text{N}_2$  and  $\text{Cl}_2/50\%\text{HBr}$  using 400W inductive power,  $-100\,\text{V}$  of dc-bias voltage, and  $10\,\text{mTorr}$  of operational pressure are shown in Figs. 1(a) and 1(b), respectively.

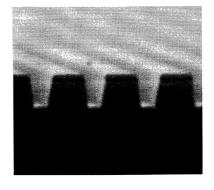

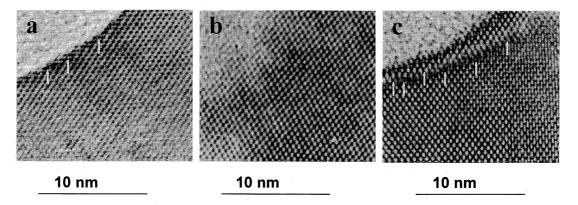

Energetic ion bombardment to the silicon from the plasma during the dry etching could cause electrical and physical damages on the exposed silicon surface. Especially when the silicon trenches are etched, there is no etch stop, therefore, the silicon trench surfaces are exposed to the plasma and are liable to get damaged from the energetic ion bombardment. The physical damage investigated using HRTEM for the silicon trenches etched 5,000 Å deep using the etching conditions in Fig. 1 showed the physical defects located up to 100 Å deep from the etched silicon surface. The use of Cl<sub>2</sub>/ 50%HBr as the silicon trench etch gas combination showed the more defects compared to Cl<sub>2</sub>/10%N<sub>2</sub> and the results are shown in Figs. 2(a) for  $Cl_2/10\%N_2$  and 2(b) for  $Cl_2/50\%HBr$ . As shown in Figs. 2(a) and 2(b), defects were found near the etched silicon trenches and the silicon trench etched using Cl<sub>2</sub>/50%HBr (b) contained deeper and more defects compared to the silicon trench etched using Cl<sub>2</sub>/10%N<sub>2</sub> (a). In case of the silicon trench etched in Cl<sub>2</sub>/50%HBr, the trench bottom edge area was even amorphized possibly due to hydrogen implantation and diffusion. In the plasmas used in our experiments, reactive ions such as Cl<sup>+</sup>, Cl<sub>2</sub><sup>+</sup>, H<sup>+</sup>, N<sup>+</sup>, Br<sup>+</sup>, etc. can exist and these species will bombard the silicon surfaces with the sheath potential higher than 100V. The etch species such as Cl<sup>+</sup>, Cl<sub>2</sub><sup>+</sup>, and Br<sup>+</sup> can damage the silicon surface through the ion bombardments, however, these species will also etch away the damaged silicon surfaces. Therefore the physical damage from these species may not high enough to be noticed. In case of H+ and N+, due to the small masses compared to the other gas species, they can penetrate deeper and also they do not etch the silicon chemically, therefore, could induce significant defects on the silicon surface. Especially the high concentration of hydrogen atom can diffuse into the silicon and can induce deep defects related to hydrogen, which are located deeper than hydrogen implantation depth due to the energetic ion bombardment as shown in Fig. 2(b).

In this study, to study effective methods in removing the defects formed during the etching with different gas combinations, the effects of oxidation and/or annealing on the removal of the remaining defects were investigated.

### 3.1 Oxidation effect

In general, during the shallow trench isolation, about 200 Å of thermal oxide (sacrificial oxide) is grown on the etched silicon trench surface and etched off to remove defects formed during the etching process and also to make the trench corners round. To study the effect of oxidation on the removal of the defects generated during the etching, 5000 Å deep silicon trenches etched using Cl<sub>2</sub>/50%HBr and Cl<sub>2</sub>/10%N<sub>2</sub> were oxidized at 900°C in O<sub>2</sub> for the time to form 200 Å thick thermal oxide on the blank silicon wafer. Figures 2(c) and 2(d) show HRTEM micrographs of silicon trenches oxidized after the etchings using Cl<sub>2</sub>/10%N<sub>2</sub> and Cl<sub>2</sub>/0%HBr at 400 W of inductive power,  $-100 \,\mathrm{V}$  of bias voltage, and at 10 mTorr of operational pressure. The 200 Å thermal oxidation of silicon consumes about 100 Å of silicon surface. Therefore, all of the physically damaged layers have to be consumed after the oxidation for both of the trench surfaces if 200 Å of thermal

(b)  $---0.5 \, \mu \text{m}$

Fig. 1. Etch profiles of 0.3-  $\mu$ m-wide silicon trenches etched with (a) Cl<sub>2</sub>/10%N<sub>2</sub> and (b) Cl<sub>2</sub>/50%HBr. Process conditions: 10 mTorr, 400 W inductive power and -100 V bias voltage.

Fig. 2. High resolution TEM micrographs of the bottom edge region of 0.3  $\mu$ m width silicon trenches (a) etched in Cl<sub>2</sub>/10%N<sub>2</sub>, (b) etched in Cl<sub>2</sub>/50%HBr, (c) oxidized at 900°Cafter the etching in Cl<sub>2</sub>/10%N<sub>2</sub>, (d) oxidized at 900°C after the etching in Cl<sub>2</sub>/50%HBr and (e) oxidized at 1,100°C after the etching in Cl<sub>2</sub>/50%HBr. Silicon trench etchings were performed at 400 W of inductive power, -100 V of dc bias voltage, and 10 mTorr of operational pressure to form 5,000 Å deep silicon trenches. The oxidation was carried out in O<sub>2</sub> for the time to form 200 Å of thermal oxide on the blank silicon wafer.

oxide was formed. However, as shown in Figs. 2(c) and 2(d), not all of the physically damaged layers were removed after the oxidation for both of the cases, and the damages from 20 Å to 40 Å thick were remained. One of the possible reasons for the remaining damage could be originated from the effect of structure on the oxidation, that is, the concave edge of silicon is generally oxidized less than the sidewall and bottom of the silicon trench due to the lack of oxidant or the enhanced compressive stress at the concave edge of the silicon trench during the oxidation. Therefore, even though the sidewall and bottom area of silicon trench consumed 100 Å thick silicon during the 200 Å thermal oxidation, less than 100 Å of silicon is consumed during the oxidation process, and physical defects can remain for both the oxidized silicon trenches as shown in Figs. 2(c) and 2(d). However the thickness of the remain-

ing damaged layer was thicker for the silicon etched using  $\text{Cl}_2/10\%\text{N}_2$  compared to that for the silicon etched using  $\text{Cl}_2/50\%\text{HBr}$ . Also even though the thermal oxidation temperature was increased to 1,100°C, the physical defects were still remained as shown in Fig. 2(e) for the silicon trench oxidized 200 Å thick at 1,100°C in  $\text{O}_2$  after the etching in  $\text{Cl}_2/50\%\text{HBr}$ .

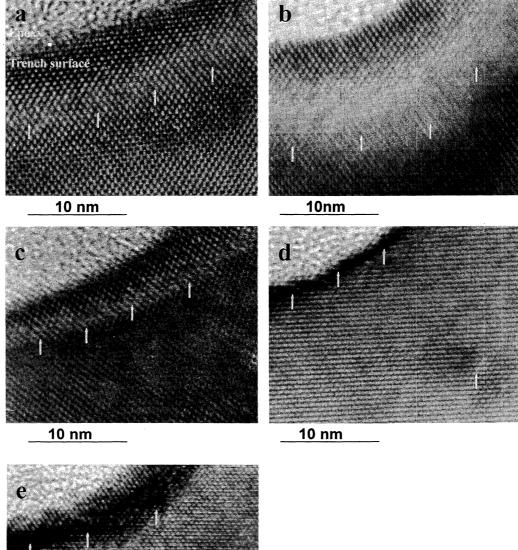

To study the reason for the thicker damage remaining on the silicon trench etched using  $\text{Cl}_2/10\%\text{N}_2$  after the same oxidation process, a blank silicon wafer was etched using  $\text{Cl}_2/10\%\text{N}_2$  while other etch parameters were kept the same as the silicon trench etch condition and the etched silicon surface was examined using XPS. The result is shown in Fig. 3. XPS data examined for the silicon wafers etched using  $\text{Cl}_2/30\%\text{N}_2$  and  $\text{Cl}_2/50\%\text{N}_2$  were also included as a comparison. As shown in Fig. 3, all of the etched wafers showed a

Fig. 3. XPS narrow scan spectra of N 1s peak etched using  $Cl_2/10\%N_2$ ,  $Cl_2/30\%N_2$ , and  $Cl_2/50\%N_2$ .

N 1s peak on the etched silicon surface. The atomic percent of nitrogen found on the silicon surface was about 2% for  $\text{Cl}_2/10\%\text{N}_2$ , and about 4% for  $\text{Cl}_2/30\%\text{N}_2$  and  $\text{Cl}_2/50\%\text{N}_2$ . The binding energy of N 1s was corrected using a C ls peak (284.5 eV) and was 399.4  $\pm$  0.3 eV. It is reported that N 1s XPS peak from N–Si<sub>3</sub> bonding is located at 397.7  $\pm$  0.2 eV and that from  $\text{SiO}_x\text{N}_y$  bonding is at 399.6  $\pm$  0.2 eV<sup>9</sup>). Therefore, the N 1s peak found on the silicon surface etched using  $\text{Cl}_2/\text{N}_2$  appears to be from  $\text{SiO}_x\text{N}_y$ . The source of the oxygen found on the silicon is partially from air exposure, however, it is more attributable from the oxygen emitted from the ICP quartz window even though no oxygen was added to the etch gas mixture. The ICP window required for generating inductively coupled plasmas in our etch system is eroded during the etching due to the high voltage generated on the ICP coil.

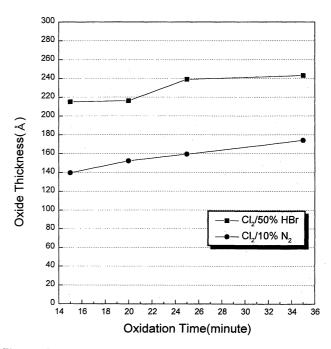

Blank silicon wafers etched using the silicon trench etch conditions (Cl<sub>2</sub>//10%N<sub>2</sub> and Cl<sub>2</sub>/50%HBr) were oxidized at 900°C in O<sub>2</sub> for different time periods and the thickness of the grown oxide was measured, and the result is shown in Fig. 4. The thickness of thermal oxide grown on the silicon wafers etched using Cl<sub>2</sub>/10%N<sub>2</sub> was much thinner than that for Cl<sub>2</sub>/50%HBr and the thickness of oxide grew with increasing oxidation time for both of the cases indicating some kind of mechanism blocking the oxidation for Cl<sub>2</sub>/10%N<sub>2</sub> at the initial stage of oxidation. The mechanism appears to be related to Si-O-N bondings found on the silicon surface in Fig. 3 because silicon oxynitride is possibly oxidized slower than silicon. In fact, silicon nitride is generally used for the oxidation mask for the conventional LOCOS process due to the about 20 times slower oxidation of silicon nitride compared to the oxidation of silicon. Therefore, the thin silicon oxynitride formed on the silicon surface during the etching with Cl<sub>2</sub>/10%N<sub>2</sub> could also block the oxidation of silicon similar to silicon nitride even though the oxidation of silicon oxynitride is faster than conventional silicon nitride. Even though the analysis in Fig. 3 and Fig. 4 were done with blank silicon

Fig. 4. Oxide film growth as a function of oxidation time (900°C,  $O_2$ ) on etched silicon surfaces with 90%Cl<sub>2</sub>/10%N<sub>2</sub> and 50%Cl<sub>2</sub>/50%HBr.

wafers not with the silicon trench patterned wafers, the same conjecture could be made for the silicon trenches etched using Cl<sub>2</sub>/10%N<sub>2</sub>. In fact, Uetake et al. reported the increase of n<sup>+</sup> polysilicon etch anisotropy by adding nitrogen to chlorine. 10) That is, by adding 10%N<sub>2</sub> to chlorine, a Si-N layer is formed on the etched n<sup>+</sup> polysilicon surface and protects the sidewall of the etched n<sup>+</sup> polysilicon from the etching. Therefore, in the case of our experiment for the silicon trench etching with Cl<sub>2</sub>/10%N<sub>2</sub>, a Si-O-N layer may be formed on the silicon trench surface. The more defects found for the oxidation of the silicon trenches etched with Cl<sub>2</sub>/10%N<sub>2</sub> compared to that with Cl<sub>2</sub>/50%HBr in Fig. 2(c) appear to be related to the possible Si-O-N layer formed on the trench, therefore, not enough oxidation may have been processed to remove all of the damaged layers for Cl<sub>2</sub>/10%N<sub>2</sub> in our experimental condition.

## 3.2 Annealing effect

The defects formed during the silicon trench etching could be also removed by annealing the etched silicon wafers after the etching. Therefore, the silicon trenches etched using both of the silicon trench etch conditions were annealed using a three-zone tube furnace in  $N_2$  for 30 min at the temperature ranges from 900°C to 1,000°C, and the physical defects remaining on the silicon trenches were observed using HRTEM.

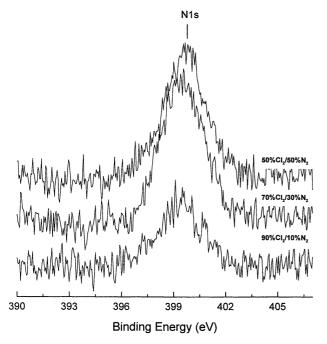

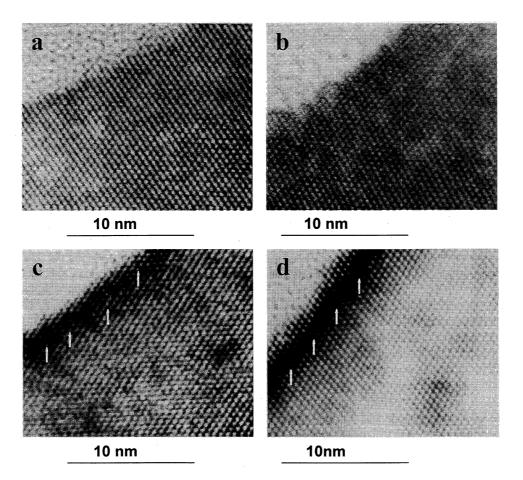

Figures 5(a) and 5(b) shows HRTEM micrographs of the silicon trenches annealed at  $1,000^{\circ}\text{C}$  for  $30\,\text{min}$  in  $N_2$  after the etchings using (a)  $\text{Cl}_2/10\%\text{N}_2$  and (b)  $\text{Cl}_2/50\%\text{HBr}$ . The silicon trench annealed after the etching with  $\text{Cl}_2/10\%\text{N}_2$  shows a clean silicon trench surface except one or two distorted atomic layers on the surface. In case of the silicon trench annealed after the etching with  $\text{Cl}_2/50\%\text{HBr}$ , a defect-free clean silicon trench surface was obtained. Silicon trenches annealed at  $900^{\circ}\text{C}$  after the etching with  $\text{Cl}_2/10\%\text{N}_2$  were also observed using HRTEM and are shown in Fig. 5(c). As shown in the figure, physical defects were still remained and

Fig. 5. High resolution TEM micrographs of the silicon trench bottom edges annealed at  $1000^{\circ}$ C in  $N_2$  for 30 min after the etchings. (a)  $1,000^{\circ}$ C anneal after the etching in 90%Cl<sub>2</sub>/10%N<sub>2</sub>, (b)  $1,000^{\circ}$ C anneal after the etching in 90%Cl<sub>2</sub>/10%N<sub>2</sub>.

Fig. 6. High resolution TEM micrographs of the silicon trench bottom edges annealed in  $N_2$  for 30 min followed by thermal oxidation of 200 Å in  $O_2$  at 900°C after the etchings. (a) 1,000°C anneal after the etching in  $Cl_2/50\%HBr$ , (b) 1,000°C anneal after the etching in  $90\%Cl_2/10\%N_2$ , (c) 900°C anneal after the etching in  $Cl_2/10\%N_2$  and (d) 900°C anneal after the etching in  $Cl_2/10\%N_2$ .

more defects were observed compared with the annealing at  $1,000^{\circ}\text{C}$  shown in Fig. 5(a) due to the lower annealing temperature. From the results from Fig. 5, to completely remove the defects formed on the etched silicon trenches by annealing, the annealing above  $1,000^{\circ}\text{C}$  for  $30\,\text{min}$  in  $N_2$  appears to be required.

Finally, the effects of combined processes of annealing and oxidation on the removal of defects on silicon trenches were investigated. After the annealing at 1,000°C for 30 min in  $N_2$  of the silicon trenches etched using  $Cl_2/10\%N_2$  and  $Cl_2/10\%N_2$

50%HBr, therefore, after removing most of defects formed during the etching by annealing, the silicon trenches were oxidized at 900°C in  $O_2$  to form 200 Å thick thermal oxide. HRTEM micrographs of these annealed and oxidized silicon trenches were observed and are shown in Fig. 6 for (a)  $Cl_2/50\%$ HBr and (b)  $Cl_2/10\%N_2$ . As shown in the figures, clean silicon trench areas were obtained for both of the etching conditions. The etched silicon trenches were also oxidized at 900°C in  $O_2$  after the annealing at 900°C for 30 min in  $N_2$ , and the results are shown in Fig. 6(c) for  $Cl_2/50\%$ HBr

and Fig. 6(d) for Cl<sub>2</sub>/10%N<sub>2</sub>. As shown in the figures, physical defects were still remained for both of the cases. Therefore, by the combination of appropriate annealing and oxidation processes, the damage formed during the trench etch processes could be completely removed.

#### 4. Conclusion

In this study, the effects of oxidation, annealing, and combined processes of annealing and oxidation on the removal behavior of physical defects formed during the silicon trench etch processes using  $\text{Cl}_2/10\%\text{N}_2$  and  $\text{Cl}_2/50\%\text{HBr}$  were investigated.

When the etched silicon trenches were oxidized in O<sub>2</sub> for the time to form 200 Å thick thermal oxide on the blank silicon wafers and were observed using HRTEM, defects were still found on the oxidized silicon trenches. In addition, more defects were observed on the silicon trench etched using Cl<sub>2</sub>/10%N<sub>2</sub> compared to that etched using Cl<sub>2</sub>/50%HBr even though more defects were found on the silicon trench etched using Cl<sub>2</sub>/50%HBr before the oxidation. The more defects found after the oxidation for the silicon trench etched using Cl<sub>2</sub>/10%N<sub>2</sub> appear to be releated to the thinner oxide formation by a Si-O-N layer found on the etched silicon wafer. The Si-O-N layer on the etched silicon wafer appears to block the initial stage of oxidation, therefore, it reduces the thickness of thermal oxide during the oxidation process, and makes it impossible to consume all of the damaged silicon trenches compared to the case of Cl<sub>2</sub>/50%HBr.

The etched silicon wafers were annealed from 900°C to 1,000°C for 30 min in N<sub>2</sub> using a tube furnace and the effects of annealing on the removal of defects were investigated

using HRTEM. The results showed that the increase of annealing temperature decreased the number of defects and the complete removal of the defects generated during the trench etch processes used in the experiment required the annealing above 1,000°C.

Complete removal of defects formed during the etchings with both  $\text{Cl}_2/10\%\text{N}_2$  and  $\text{Cl}_2/50\%\text{HBr}$  could be obtained by using a combined process of annealing at 1,000°C for 30 min and oxidation at 900°C to form 200 Å thick thermal oxide.

#### Acknowledgements

This study was supported by the academic research fund of Ministry of Education, Republic of Korea, through Inter-University Semiconductor Research Center (ISRC 97-E-1038) in Seoul National University.

- B. Davari, C. Koburger, T. Furukawa, Y. Taur, W. Noble, A. Megdanis, J. Warnock and J. Mauer: IEDM Tech. Dig. (1988) p. 88.

- A. Chatterjee, J. Esquivel, S. Nag, I. Ali, D. Rogers, K. Taylor, K. Joyner, M. Mason, D. Mercer, A. Amerasekera, T. Houston and I. Chen: 1996 Symp. VLSI Technology Dig. Tech. Pap. (1996) p. 156.

- 3) J. Y. Cheng, T. F. Lei and T. S. Chao: Jpn. J. Appl. Phys. 36 (1996) 1319.

- 4) H. Crazzolara and N. Gellrich: J. Electrochem. Soc. 137 (1990) 708.

- J. Maa, H. Gossenberger and L. Hammer: J. Vac. Sci. Technol. B 8 (1990) 581.

- 6) M. Sato and Y. Arita: J. Electrochem. Soc. 134 (1987) 2856.

- S. Samukawa, M. Sasakai and Y. Suzuki: J. Vac. Sci. Technol. B 8 (1990) 1192.

- J. H. Lee, G. Y. Yeom, J. W. Lee and J. Y. Lee: J. Vac. Sci. Technol. A 15 (1997) 573.

- 9) S. R. Kaluri and D. W. Hess: J. Electrochem. Soc. 145 (1998) 662.

- 10) H. Uetake, T. Matsuura, T. Ohmi, J. Murota, K. Fukuda and N. Mikoshiba: Appl. Phys. Lett. 57 (1990) 596.